Триггер.

Для реализации хранения данных в оперативной памяти компьютера и внутренних регистрах процессора необходимо устройство способное находится в двух устойчивых состояниях (0 и 1). Такое устройство было изобретено советским ученым-радиотехником Михаилом Александровичем Бонч-Бруевичем в 1918 году на основе лампового триода. В последствие этот элемент получил название триггер (англ.trigger – «спусковой крючок», в общем смысле, приводящий нечто в действие).

Триггер - устройство, способное длительное время находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов.

Один триггер способен хранить один бит данных. Соответственно, для хранения 1 байта информации потребуется 8 триггеров, а для 1 килобайта – 8 • 1024 подобных элемента. Очевидно, что современные объемы оперативной памяти компьютера содержат миллионы триггеров.

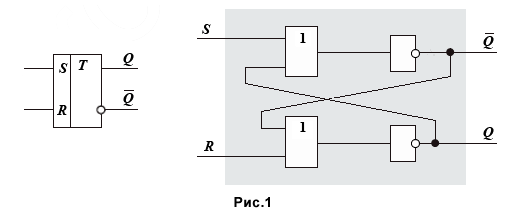

Существует несколько видов триггеров. Одним из самых распространённых является RS-триггер. Rs-триггер можно построить на двух дизъюнкторах и двух инверторах. На рисунке 1 показано условное обозначение триггера (слева) и его устройство на указанных логических элементах.

Триггер имеет два входа S (от англ. set - установить) и R (от англ. reset - сброс), на которые поступают управляющие сигналы и два выхода - Q и ¬ Q. Основным выходом является Q.

Для реализации возможности хранения информации в устройстве триггера используется обратная связь. Под обратной связью понимают подачу выходного сигнала на вход устройства. Обратная связь имеет перекрестный характер (см. рис.1). Дополнительный выход ¬ Q используется только для обратной связи.

Построим таблицу истинности для триггера.

- S = 0, R = 0. В этом случае на вход элемента «ИЛИ» в нижней ветке поступит сигнал ¬ Q + 0 = ¬ Q. Значит, на выходе Q остается прежнее значение. Аналогично, нетрудно заметить, что сигнал ¬ Q также не меняет своего значения. Таким образом, в данном режиме триггер хранит предыдущее состояние.

- S = 0, R = 1. Т. к. на вход R поступает 1, то на выходе элемента «ИЛИ» в нижней ветке схемы будет 1, а на выходе «НЕ» - ноль. Значит, Q = 0. Тогда на входы элемента «ИЛИ» в верхней ветке поступает два нуля, а на выходе ¬ Q имеем 1. Выход Q является основным, значит, в триггер записан 0.

- S = 1, R = 0. В силу симметрии схемы (см. рис.1), легко заметить, что в этом случае в триггер будет записана 1.

- S = 1, R = 1. Такая комбинация входных сигналов может привести к неоднозначному результату, поэтому такой вариант запрещен.

| S | R | Q | ¬ Q | Режим работы триггера |

|---|---|---|---|---|

| 0 | 0 | Q | ¬ Q | Хранение бита |

| 0 | 1 | 1 | 0 | Сброс в 0 |

| 1 | 0 | 0 | 0 | Установка в 1 |

| 1 | 1 | 1 | 1 | Запрещено |